11:10 Экономичный стабилизатор напряжения | |

|

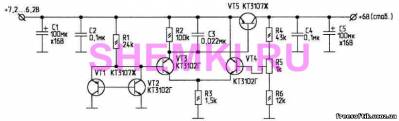

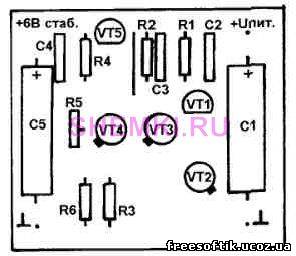

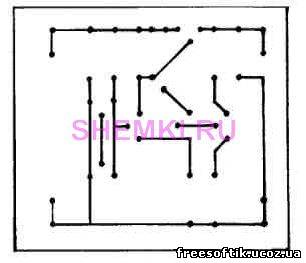

Автор разработки: О.Белоусов Схема принципиальная Экономичный стабилизатор напряженияПредлагаемая схема стабилизатора (рис.1) имеет высокий КПД — порядка 93% (при токе нагрузки 20 мА) и потребляемый ток — всего 0,7 мА. Это достигается тем, что стабилизатор построен по схеме "с малым напряжением потерь", и в качестве элемента стабилизации применен аналог низковольтного стабилитрона. Минимальный ток стабилизации, по утверждению автора - «Аналоги низковольтных стабилитронов - схемы, описания, справочные материалы», составляет 0,1 мА. Стабилизатор построен по компенсационной схеме. С аналога низковольтного стабилитрона на VT1, VT2 опорное напряжение 1,25 В подается на неинвертирующий вход дифференциального каскада (VT3), на инвертирующий вход (VT4) которого подается напряжение с делителя напряжения, подключенного к выходу стабилизатора. Сигнал рассогласования поступает на регулирующий транзистор VT5. Регулирующий транзистор включен по схеме с общим эмиттером по отношению к нагрузке. В данной схеме включения минимальное падение напряжения на транзисторе составляет 0,2 В. Поэтому минимальная разность между входным и выходным напряжениями стабилизатора равна этой величине. Конденсатор С3 необходим для предотвращения релаксационных колебаний. Сборочный чертеж и рисунок печатной платы приведены соответственно на рис.2 и 3. Данный стабилизатор используется в портативной радиостанции личного пользования.

Поделись с друзьями в социальных сетях Реклама Похожие материалы: | |

|

| |

| Всего комментариев: 0 | |

Дорогие друзья!

Если у Вас есть желание поделится своими разработками, присылайте их мне на почту

Материал должен состоять из названия, схемы, описания с указанием имени автора, прошивки (если есть) и фото внешнего вида разработанного устройства.

Интересные разработки поощряются материально!

Здравствуй Гость, как Вы видите еще никто не оставил свой комментарий, будьте первым, поделитесь мнением о материале выше.